이번 글부터는 직접 어떻게 제작했는지에 대해 설명해 보겠습니다! 물론 제가 만든 건 아니고 대학원 조교님들이 만들어주신 거라 정확한 공정 팁이나 이런 건 없지만 공정조건에 따른 특성분석을 진행했구나라고 생각하고 봐주세요.

1. CMOS recipe

0. wafer - P-Si

1. wafer cleaning - acetone sonic 1min, methanol sonic 1 min, DI water sonic 1 min (sonicator사용)

2. thermal ALD - TEMAHf (precursor), ozone (reactant) / stage temperature 320ºC HfO2 10.2nm --> precursor feeding time 1.5s, reactant time 30s / 67 cycle HfO2 23.8nm --> precursor feeding time 1.5s, reactant time 30s / 155 cycle

3. DC power magnetron sputter (top electrode) - W 35nm, TiN 35nm / Ar plasma

4. Forming gas annealing(FGA) - H2 4% + N2 96% gas / 400 ºC 30 min

이게 제가 진행한 프로젝트의 HKMG CMOS소자 제작 간 주요 과정에 대한 recipe입니다. 이는 주요한 과정에 대한 recipe이고 자세한 CMOS제작과정이나 photo 하나하나는 지난 게시글에 올려두었던 두 번째 사진 밑에 출처를 보시면 굉장히 자세히 나옵니다! 그럼 이제 시작해 볼게요!

2. 제작 과정 설명

- 0번 1번 우선 P형 기판의 Si을 사용했습니다. 보통 전자와 정공 중 전자의 이동속도가 빨라 보통 P형 기판, 즉 N형 반도체를 사용합니다. 이후 클리닝을 거치고 이후에 Pwell 만들고 하는 과정이 있었을 것입니다. 저는 이후 Oxide layer 만드는 과정으로 넘어가겠습니다.

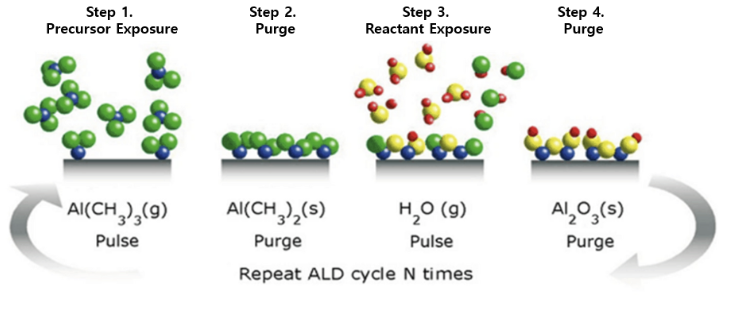

- 2번 이후 저희는 Thermal ALD를 활용해 HfO2를 Oxide layer로 증착했습니다. TEMAHF을 precursor로 oznoe을 reactant로 사용했습니다. 여기서 살짝 설명을 드리자면 ALD의 precursor와 reactant는 CVD에서의 precursor와 똑같습니다. 다만 ALD는 아시는 것처럼 순서를 구분해서 precursor를 넣어주기 때문에 구분하기 편하게 둘로 나누어 부릅니다. TEMAHF을 통해서 Hf을 O3를 통해서 HfO2를 증착한다고 생각하시면 될 거 같습니다.

- 2-1번 ALD 특징 : ALD 레시피를 보면 특이한 점이 있는데요. 뭘까요? 바로 10nm와 20nm의 cycle 차인데요. 10nm를 보면 67회인데 20nm는 그 2배인 134회가 아닌 155회라는 점입니다. 물론 결과가 23.8nm로 목표였던 20nm보다는 조금 더 증착됐지만, 실제로도 항상 증착 두께가 두꺼워질수록 cycle을 더 많게 해줍니다. 왜냐하면 두께가 두꺼워질 수록 GPC(Growth Per Cycle)이 작아집니다. 그 이유는 꽤나 다양한데 공정적인 측면에서 보자면 아래그림과 같습니다.

왼쪽 그림이 처음 ALD 공정을 공부할때 많이들 접하는 그림일텐데요, 실제로는 오른쪽과 같습니다. 즉 정확히 formal 하게 평평한 박막을 증착할 수 없다는 거죠. 그래서 1cycle을 돌리고 난뒤에 오쪽 그림위에 다시 증착을 하게되면 비어있는 부분에 증착을 하게되면서 예상보다 조금 덜 증착되게 되는거죠.

- 2-2번 feeding time v.s reactant time : feeding time과 reactant time이 이름이 달라 뭔가 다른 공정같지만, 사실 그냥 precursor를 넣어주는지, 아니면 reactant를 넣어주는지에 대한 차이일 뿐입니다. 그러면 왜이렇게 차이가 많이나냐? 여러가지 이유가 있습니다. 우선 가장 큰 이유는 기판과 precurosr는 굉장히 흡착이 빠르게 진행됩니다. 또한 많이들 들어봤을 Self limiting 반응을 하기 때문에 긴 시간 feeding 하는 것이 의미가 없기 떄문도 있습니다. 반면 reactant time의 경우 기판이 아닌 흡착되어 있는 전구체와 반응을 해야되기 때문에 반응시간이 좀 더 걸립니다. 위 실험 역시 산화막을 형성하는 과정이다 보니 오존을 넣어주는데 오존의 경우 반응성이 높지 않기 떄문에 좀 더 시간이 걸렸다고 보시면 될 것 같습니다.

- 3번 다음으로는 전극을 만들어줘야 합니다. 전극은 sputter로 증착을 진행하였고 W과 TiN를 섞어 사용했습니다. W의 경우는 낮은 저항과 열적 안정성, 그리고 기계적 강도가 좋아 전극으로 채택되었습니다. 하지만 W의 경우 HfO2 내부로 원자가 침투하기도 하고, HfO2와의 계면 안정성이 좋지 않습니다. 이를 극복하고자 TiN를 일종의 barrier layer처럼 사용하게 됩니다.

- 4번 마지막으로 annealing 과정입니다. 반도체 공정에서 annealing 공정을 진행하는 경우는 굉장히 많습니다. 해당 과정에서 저희가 진행한 FGA는 forming gas annealing으로 산화막의 신뢰도를 높여줍니다. 표면의 dangling bond 나 산화막 내부의 trap되는 전자를 미리 막기 위해 해당 자리들을 H원자가 가서 결합을 하게 됩니다.

저희는 공정 조건 중 마지막 annealing 공정의 변화를 통해 소자의 특성을 개선할려는 프로젝트를

진행했습니다. 다음 포스팅부터는 해당 프로젝트에 대해 소개해보겠습니다! 그럼 오늘은 여기까지

'CD KIM > 반도체 기본' 카테고리의 다른 글

| CMOS 소자 제작 ③ - Annealing 공정 변화를 통한 소자 특성 개선 (2) | 2024.12.02 |

|---|---|

| CMOS 소자 제작 ① - HKMG의 필요성 (2) | 2024.12.01 |

| 관측장비의 이해④ SEM_1_Microscope의 역사와 Spacial resolution (0) | 2024.05.14 |

| 관측장비의 이해 ① X-ray diffraction(XRD)_ 원리와,Peak 그리고 다양한 factors (0) | 2024.04.07 |

| 관측장비의 이해 ① X-ray diffraction(XRD)_Kα 와 Kβ (0) | 2024.04.03 |